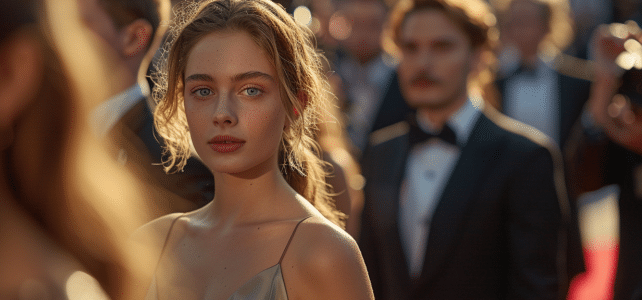

Dans le monde scintillant d’Hollywood, la célébrité peut être considérée comme un héritage, avec des dynasties d’acteurs qui captivent le public sur plusieurs générations. Les enfants de stars, nés sous les projecteurs, sont souvent scrutés et leurs parcours sont suivis…